5.3 By convention, a cache is named according to the amount of data it contains (i.e., a 4 KiB cache can hold 4 KiB of data); however, caches also require SRAM to store metadata such as tags and valid bits. For this exercise, you will examine how a cache’s confguration affects the total amount of SRAM needed to implement it as well as the performance of the cache. For all parts, assume that the caches are byte addressable, and that addresses and words are 64 bits.

بقیه سوال و حل تشریحی در ادامه مطلب مشاهده کنید...

یادداشت: حافظه های cache را معمولا بر حسب کل اطلاعاتی که ذخیره میکنند نامگذاری میکنند مثال حافظه cache چهار کیلوبایتی.

5.3.1 [10] <§5.3> Calculate the total number of bits required to implement a 32

KiB cache with two-word blocks.

راه حل:

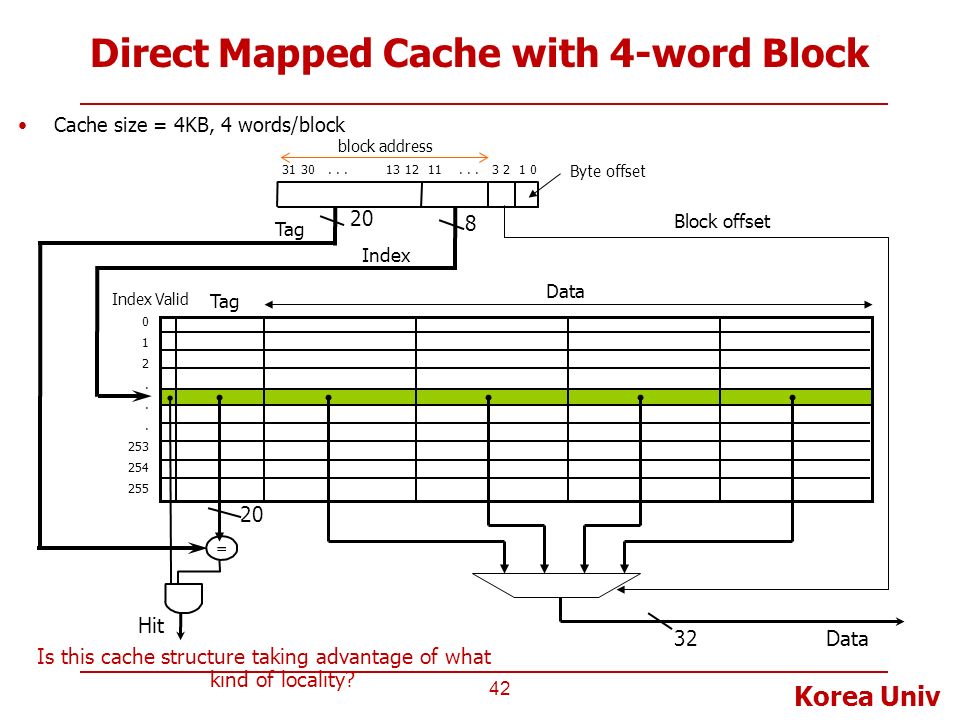

در سوال به ما گفته شده که حافظه 32 کیلوبایتی است، که با آن میتوان تعداد کل بلاک های حافظه را به دست آورد. دقت کنید که در متن سوال آمده که هر کلمه یا word تشکیل شده از 8 بایت است. حال میتوانیم تعداد کل بلاکهای حافظه cache را به دست آوریم:

1 block = 2 word = 16 Bytes

32KiB = 4 × 1024 words = 212 words = 211 blocks

حالا که دو به توان یازده بلاک داریم پس برای شماره گذاری این تعداد بلاک باید 11 بیت اختصاص دهیم، نام بیت هایی که برای شماره گذاری cache در نظر میگیریم، index است:

index bits = 11bits

خب هر بلاک حافظه cache شامل 2 کلمه یا word میشود، دقت کنید که در اطلاعات سوال آمده بود که نوع آدرس دهی حافظه به هر Byte است و چون هر

Bytes offset = 4bits

tag size = 64 - 11 - 4 = 49

block size = 2 × 8 Bytes = 16 × 8 bits = 128 bits

Te total number of bits in a direct-mapped cache is: (number of blocks) × (block size + tag size + valid bit)

=> 211 × (128 + 49 + 1) bits = 178 × 211 bits = 365 × 210 bits = 365 Kibits

------------------------------

5.3.2 [10] <§5.3> Calculate the total number of bits required to implement a

64 KiB cache with 16-word blocks. How much bigger is this cache than the 32

KiB cache described in Exercise 5.3.1? (Notice that, by changing the block size, we

doubled the amount of data without doubling the total size of the cache.)

>> solution:

1 word = 8 Bytes

1 block = 16 words

64KiB = 8 × 1024 words = 213 words = 29 blocks

index bits = 9bits

Bytes offset = 7bits

tag size = 64 - 9 - 7 = 47

block size = 16 × 8 Bytes = 210 bits = 1024 bits

Te total number of bits in a direct-mapped cache is: (number of blocks) × (block size + tag size + valid bit)

=> 29 × (1024 + 47 + 1) bits = 536 \times 210 bits = 536 Kibits

===> 536/365 = 1.46 times more bits for 64KiB cache.

5.3.3 [5] <§5.3> Explain why this 64 KiB cache, despite its larger data size, might

provide slower performance than the first cache.

5.19 Exercises 499

>> solution:

more block size -> less block number -> more miss-rate

5.3.4 [10] <§§5.3, 5.4> Generate a series of read requests that have a lower miss

rate on a 32 KiB two-way set associative cache than on the cache described in

Exercise 5.3.1

>> solution:

to do...

منبع سوال: کتاب Computer Organization and Design ARM® EDITION